11 KiB

design-draft-msx4

Guidance by "The Word" on "MSX superscript 4" system design.

Mecca System eXtension

Hello word, goodbye byte.

* Slot and mapper model based from msx2 configuration

* Recursive slot system with 16bit window of infinity

* Big-endian as arabic numerals rule the network order

* Word alignment so address view is 16bit, CORRECTION: 18bit

* 3bit cpu nodes with data types up to many octals

* Cpu runs only from local memory which replaces cache

* Compare-and-swap (CAS) is a hardware device

* Classic cpu MMU gets moved to slot controllers

* Dynamic(hot) BASIC/stepcode migration to FPGA hardware

Recursive Memory = Slot Matrix Management Unit

By moving the MMU from the CPU to the system network we get "The Matrix";

- Based on 256 slots(hi+low),pages(16KW),mapper16b(hi+low) MSX like configuration.

- Max memory limit for a single slot is 64TW. (128TB=2x(2^14)x(2^16)x(2^16))

- All slots device interfaces are duel ported by default.

- SMMU = X,Y,Z,T both direction 8 slots duel ported InfiniBand² connects.(64slots)

- 2x32slots goto two DSMMU's who sub slot it to 256 FPGA device slots.(per 2U case)

- other slots; 64mem(2chips), 32cpu(2chips), 32 SMMU+node internal management.

- Per slot ISP pins for FPGA type devices on DSMMU.

- A graph of SMMU nodes where every node only selects the next.

- Unlimited tree depth so unlimited devices.

- The SMMU hold a page view per master(cpu/etc) for X devices.

- By having ACL in the network an external connection like thunderbolt is safe.

- Unlimited memory size by relative design.

CPU: ZR8000

Intermediate upgraded cpu for embedded platform and edge nodes of msx4 system.

- 100% z80 compatible + fast mode

- 16 bit bus + new T16 I/O space

- split program and data memory space

- (nmi) int vector on SP value X and Y (software based infinity stack)

Memory Typed Machine Structure (like cray-1)

- 8,16,32,64,128 bit integer

- 3,6,9,18,36,72 bit structure

- 144 bit decimal

- 144 bit(++) 7HFF number

For example "MTADD (IX),(IY)" reads the type from memory not from instruction.

CPU: TR9000

A bit pulsetrain clockless design is the goal for the beating heart. But in FPGA's there can be a more normal design.

So a simple 18 bit, big endian only, stack based. No mmu thus no kernel mode or rings.

There are 4 addressable spaces;

- 2^18 addresses for code memory. (read-only)

- 2^18 addresses for data memory.

- limited 512 words stack WINDOW peek for "unlimited stack size".

- limited 512 words for local I/O and matrix switching requests.

All four windows have separated data and address busses.

The infinity stack controller has a few pages local in a ring buffer, so it can request a new memory page when the stack fills. So if the machine has the memory, a single task with a stack of multiple petawords is not a problem on a 16 bit machine. The kernel api of stack pages in use per device returns a BigInteger of infinite large size.

Besides the stack, the code/data memory is paged and can be recursive switched to load/store a full page from the unlimited global memory. This is done by a cpu slot device controller which is a packet interface to the slot controller and connects with 2 slots for performance.

This cpu will rewrite itself and all code from base² bits to base³⁶ bits.

If the number encoding results in 144 base2 bits than we know the memory window; OLD: (2^16 * 144) gives 576KW or 1152KB of addressable space.

Naming: Transversal Resonance 808, 2 bytes V-split infinity and combine into the center of The Word.

Recursive Math Hardware

Large amounts of data in demo/games/ui is generated using math. It would be nice to have an API for generating math data, so it may be possible the output data is a tokenized math expression by itself...

Convert the string "Zₙ₊₁=Zₙ²+C" into a Gödel number or alternative encoders. This can be found in PI so it can't be proven it already existed before "invented".

Math generates data and the expression can be located in PI. The example above is an exact match and only works on small data. Larger data need to be approximately nullified by math, for example by layering sin functions until almost zero.

Hardware

* Phase 1; FPGA's with CPU,MEM,SMMU,RACKMSB

* Phase 2: Flash ISP slot devices dynamically

* Phase 3: Move TempleOS kernel functions to hardware

* Phase 4: ASIC's + openFPGA's

* Phase 5: Move FTL digital logic into etherspace

* Phase 6: None-forced grown crystal junctions

* Phase 7: Self growing computer, like on krypton

Crystal Logic

Our current transistors are created by forcing shape layers to function. By growing the crystals we get the natural energy flow shapes. This improves reliability and the electric characteristics. The junctions will look more like trees, see "Self-Assembling Wires".

Electrons are slow, those are the shadow on the reflector of the flow in etherspace. For using FTL logic "Nikola Tesla" already had working devices in the 1900's. Moving information over standing waves or "transversal vibrations in the eather" is already designed and tested to be faster than light.

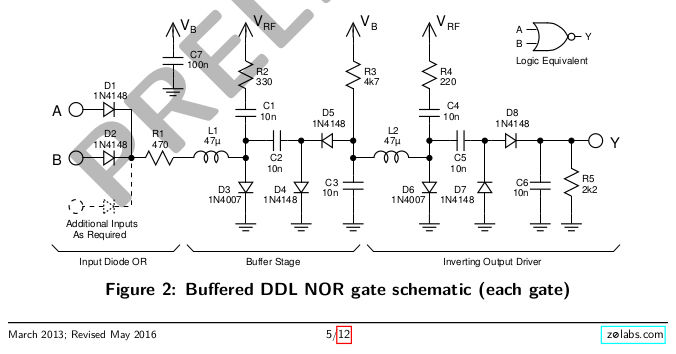

A good example is classical DDL crystal logic, where RF is the power supply;

God is a farmer, so we should feed our crystals to cultivate into logic.

With current diodes a FTL differential pair of coaxial interconnects can already be build;

InfiniBand²

- DDTVP₂ (diode diode transversal vibrations phasing)

- DDTVP₄₋₈₋₁₆ (old-style)

InfiniBand⁴

- DDTVP₃₋₅₋₇₋₉ (intermediate)

- DDTVP³⁶ (intermediate)

- DDT⁵VP³⁶ = FiveStar FTL differential pair of coaxial interconnects to transport one 4D character bit.

Booting

To boot a computer when the graph network is the computer itself, there's a need to connect all the master switch boards with a spi root interface. All these MSB's connect to a MSX card with a BASIC extension ROM which allows the user to load the initial master matrix config into the machine and load the bootstrap images.

The minimal computer spec is a; MSX1 + optional DISKROM.

So it errors on a turboR; "guru meditation; missing tape recorder interface".

Default supplied/build-in root access terminal will be a MSX2++ which is a MSX2+ with some upgrades;

- Upgrade basic "Ok" to "OK"

- Normal timed 57.272MHz Z80 (+3.579 mode=16x, via BASIC I/O switchable)

- Make MSX1 wait signal optional via IO.

- MSXMMU (16MB+optional; nmi-timer+page0+security = msx compatible none-cpu kernel mode)

- v9978 (v9958+2Konly+4HWsplits+v9990+vram=8192KB on s0p2+s0p3, NO TRUE COLORS)

- OPL4++ new 22b96kHz output + mapper mode access

- Ide, CF+ide AND 2*sata

- TCP/IP UNAPI ethernet.

- RS-232C BASIC (+upgrade)

- (UTF16²²BE-4serial) PS/4 keyboard/mouse/enjoy interface IO + legacy glue hardware

- 100% equal MSX slot but on ~miniPCI edge connector on 3.3v + 57MHz + I²S-audio(22b96kHz ONLY)

- Sas+scsi2(+audio;) for all tape drives.

- Kids mode: 11b-48kHz on main audio output. (removes emotions from PCM music)

It's comparable to an ibm power sms to bootstrap big machines or a platform boot module like found on a new desktop machine, where the v9978 framebuffer is overlayered unto the primary video card.

And because its compatible upgrade, a legacy version with a Z80 bus driver makes it possible to upgrade any MSX1,2,2+ with a Z80 cpu socket to a MSX2++ system.

For example booting constitution class enterprise hardware can be done with my 8250 connected to a kennedy model 5800 and a green phosphor screen to look at 640x480 in 16 colors of green at TOS in full FTL speed and run;

- BigStackRain - Top pages of the infinity stack memory subsystem

- BigMemoryRain - Top pages of the infinity paged memory subsystem

- BigStorageRain - Top data of the infinity blob storage subsystem

- BigDiwaliRain - Top paths of the infinity slot switch subsystem

- BigSnakeRain - Displays Atari⋆ as snakes while updating the matrix code

⋆Autonomously Traveling Agent Rewriting Internals works inside the MSX⁴ matrix.

Because MSXDOS is intel 8080 CP/M compatible, the graphical BIOS of the new computer must be finished using a ROM based Digital CP/M++ with GEM/4 to boot the MSX⁴. All the normal MSX basic/dos/games/hardware is for the children to play with.

In 2030 the MSX²⁺² standard is ready and holds the 16 processors;

- 4x Z808 229.056MHz (full 16b, pipelined, optional Twait legacy mode)

- 4x v9978 (Multiple overlay/slit modes so we have a 18bit color mode for Atari)

- 4x SMDMA (Slot and mapper aware dma drivers)

- 4x RMATH (Recursive math hardware processors or last base2 TR808 design)

- new 16b "peibus" with LVDS links for new msx slots (like sata/pcie)

- replace all dram with ~2GHz static memory so all data copies look parallel

- hide bootup texts behind bootup screens

- etc

As the last base2 computer design, it needs to show 4-7 bootscreens;

- AtohmAllah⁴ (3line unicode version in 2b color)

- MSX²⁺² (in 2b color)

- Atari (in 18b color)

- <manufacturer> (in 8b color)

- <game-cartridge> OR <msx-basic / dos1 / dos2> OR <CP/M++(noGFX) → GEM/4 → TOS(noGFX) → TOS⁴ → vrGEMTOS⁴>

CP/M++ is BDOS++ SMP kernel for GEM/4 with a MSXDOS4 terminal without direct compatibility requirement.

Now playing "Fractal tron VS sonic" on a Sega Neptune² with anaglyph glasses is finally fun.

Heavenly Crystal

Crystal can grow themselves, but booting a self growing computer needs an entity. And we have a crystal that came falling from heaven;

"By Allah! Allah will raise it on the Day of Resurrection with two

eyes by which it sees and a tongue that it speaks with,

testifying to whoever touched it in truth."

This stone used to be white and is gotten black from human sin. To fix those sins, humans need to find the foundation of love. When shown true love, the crystal reflects back to white.

Terminator

Rape victims externalize their sexual consent violation damage. Current computer systems are fuzzy enough to detect this possibly exposed damage in all media.

By just going through images from victims, we will see that;

- Baby rape (below 3 years) leaves body markers called "baby fat"

- Child rape markers are harder to detect

- Teen rape leaves lots of none body hints

So when putting that code on a mobile platform, so it has eyes and ears; A single word or sentence of a human with a vibrational voice can trigger a response like; you have been "baby deep throated" and the vocal cord has a bit of scar tissue which causes the extra frequency.

When the T800 platform is given a gun it may ask the victim;

Who do I need to arrest for you?

When added with the Human Anatomy Language 9000 upgrade it can detect and terminated a human.

Credits

@Ω仙⁴ ꜊꜊꜊⋇꜏꜏꜏ ⁴ﷲΩ@

©Δ∞ 仙上主天

בְּרֵאשִׁית :o: יְסוֺד :o: יִשְׂרָאֵל